-

- Downloads

reorg

Showing

- usb_serial/images/2023-12-27_simple-04-cobsless-d21.png 0 additions, 0 deletionsusb_serial/images/2023-12-27_simple-04-cobsless-d21.png

- wiznet_ethernet/2023-12_ethernet-real-data-rates.md 14 additions, 2 deletionswiznet_ethernet/2023-12_ethernet-real-data-rates.md

- wiznet_ethernet/code/ethernet_sink/plot_stamps.py 0 additions, 0 deletionswiznet_ethernet/code/ethernet_sink/plot_stamps.py

- wiznet_ethernet/code/ethernet_sink/sink.py 0 additions, 0 deletionswiznet_ethernet/code/ethernet_sink/sink.py

- wiznet_ethernet/code/ethernet_source/ethernet_source.ino 0 additions, 0 deletionswiznet_ethernet/code/ethernet_source/ethernet_source.ino

- wiznet_ethernet/images/2023-12-28_eth-begin.png 0 additions, 0 deletionswiznet_ethernet/images/2023-12-28_eth-begin.png

- wiznet_ethernet/images/2023-12-28_eth-oneway-64.png 0 additions, 0 deletionswiznet_ethernet/images/2023-12-28_eth-oneway-64.png

- wiznet_ethernet/images/2023-12-28_eth-ping-256.png 0 additions, 0 deletionswiznet_ethernet/images/2023-12-28_eth-ping-256.png

- wiznet_ethernet/images/2023-12-28_eth-ping-512.png 0 additions, 0 deletionswiznet_ethernet/images/2023-12-28_eth-ping-512.png

- wiznet_ethernet/images/2023-12-28_eth-ping-64.png 0 additions, 0 deletionswiznet_ethernet/images/2023-12-28_eth-ping-64.png

- wiznet_ethernet/images/2023-12-28_eth-ping-768.png 0 additions, 0 deletionswiznet_ethernet/images/2023-12-28_eth-ping-768.png

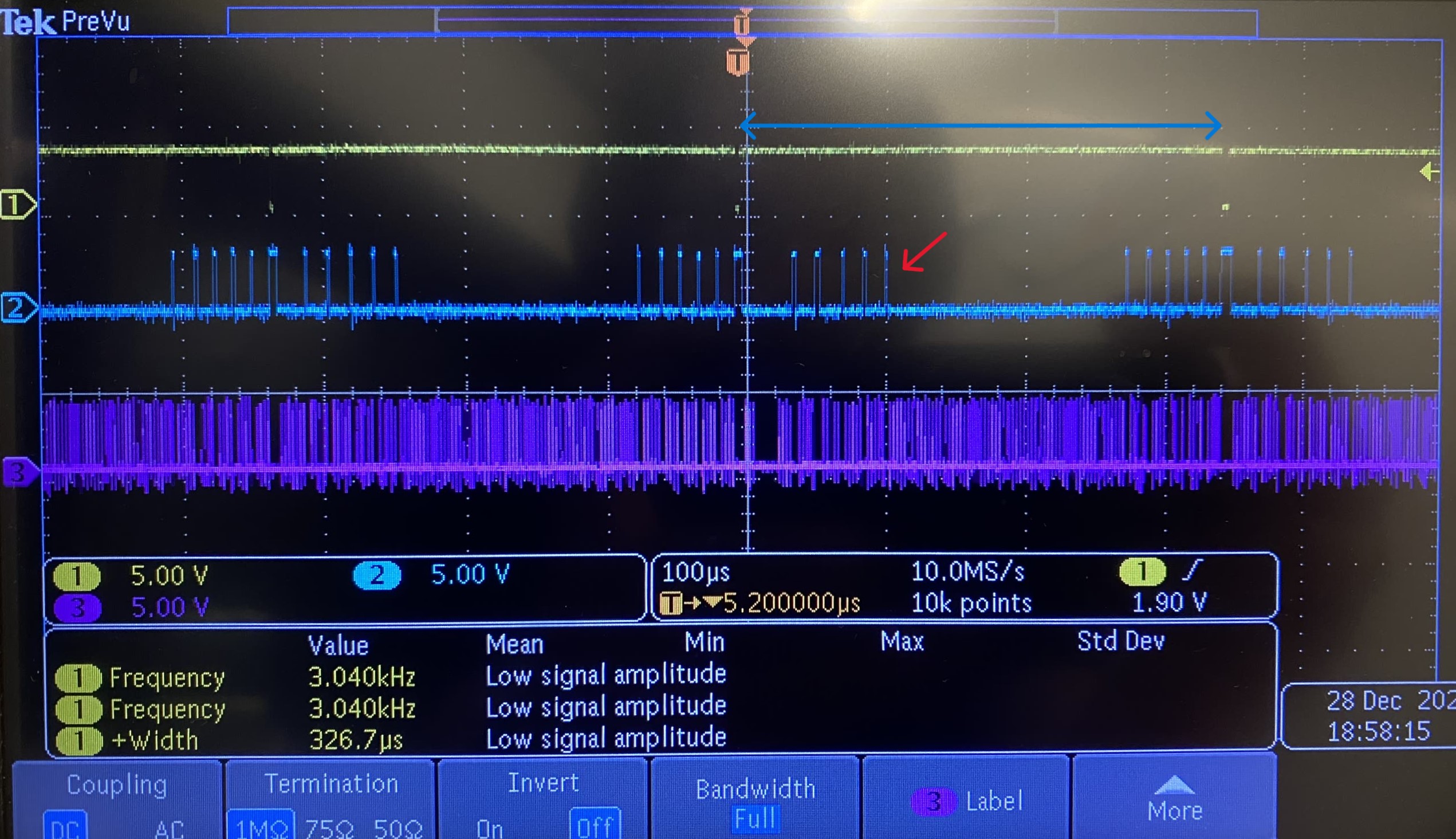

- wiznet_ethernet/images/2023-12-28_ethernet-wiz-spi-01.jpg 0 additions, 0 deletionswiznet_ethernet/images/2023-12-28_ethernet-wiz-spi-01.jpg

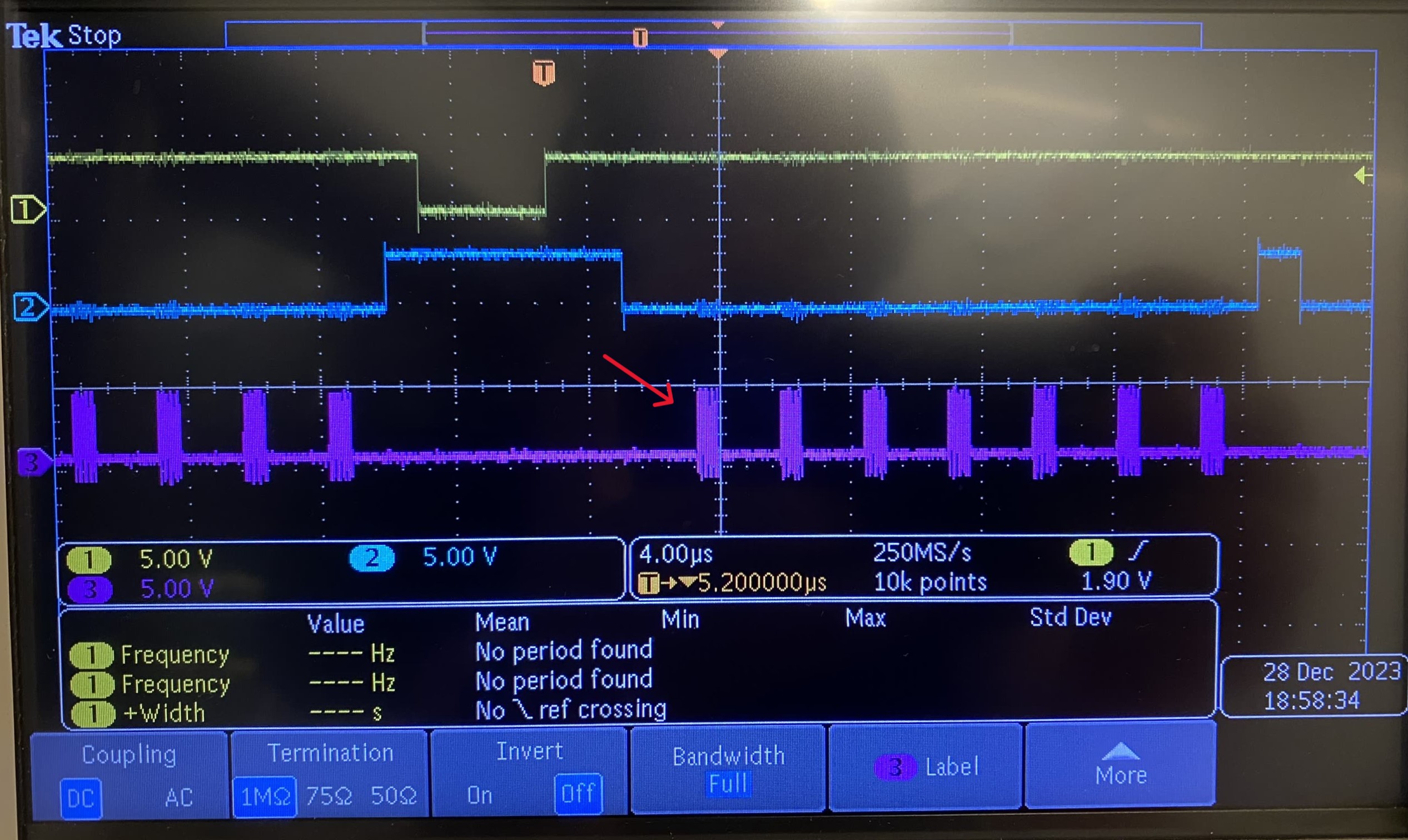

- wiznet_ethernet/images/2023-12-28_ethernet-wiz-spi-02.jpg 0 additions, 0 deletionswiznet_ethernet/images/2023-12-28_ethernet-wiz-spi-02.jpg

File moved

File moved

File moved

File moved

File moved

File moved

File moved

File moved

File moved

659 KiB

591 KiB